Product Summary

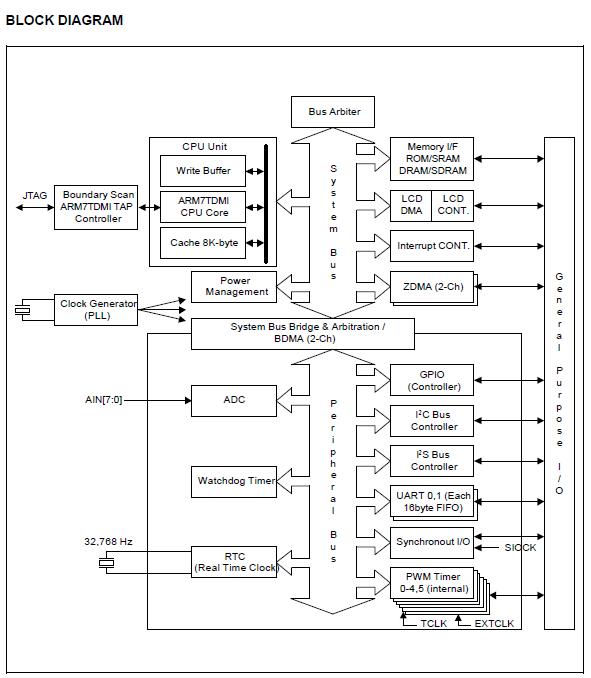

The S3C44BOX01 16/32-bit RISC microprocessor is designed to provide a cost-effective and high performance micro-controller solution for hand-held devices and general applications. To reduce total system cost, S3C44BOX01 also provides the following: 8KB cache, optional internal SRAM, LCD controller, 2-channel UART with handshake, 4-channel DMA, System manager (chip select logic, FP/ EDO/SDRAM controller), 5-channel timers with PWM, I/O ports, RTC, 8-channel 10-bit ADC, IIC-BUS interface, IIS-BUS interface, Sync. SIO interface and PLL for clock. The S3C44BOX01 was developed using a ARM7TDMI core, 0.25 um CMOS standard cells, and a memory compiler. Its low-power, simple, elegant and fully static design is particularly suitable for cost-sensitive and power sensitive applications. Also S3C44BOX01 adopts a new bus architecture, SAMBA II (SAMSUNG ARM CPU embedded Microcontroller Bus Architecture).

Parametrics

S3C44BOX01 absolute maximum ratings: (1)DC, Supply Voltage: 3.6 V; (2)VIN, DC Input Voltage: 3.3 V Input buffer to 4.6 V; (3)VOUT, DC Input Voltage: 3.3 V buffer to 4.6 V; (4)Ilatch, Latch-up Current: ± 200 mA; (5)TSTG, Storage Temperature: - 40 to 125 ℃.

Features

S3C44BOX01 features: (1)Integrated system for hand-held devices and general embedded applications; (2)16/32-Bit RISC architecture and powerful instruction set with ARM7TDMI CPU core; (3)Thumb decompressor maximizes code density while maintaining performance; (4)On-chip ICE breaker debug support with JTAGbased debugging solution; (5)32x8 bit hardware multiplier; (6)New bus architecture to implement Low-Power SAMBA II(SAMSUNG’s ARM CPU embedded Micro-controller Bus Architecture).

Diagrams

|

S3C44B0X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C4510B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C4530A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C49F9X |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))